Synopsys, Inc., the world leader in semiconductor design software, has unveiled Synopsys SpyGlass vP-2019.06 SP1.1. Using many advanced algorithms and analysis techniques, this platform provides designers with insight about their design, early in the process at RTL. It functions like an interactive guidance system for design engineers and managers, finding the fastest and least expensive path to implementation for complex SoCs.

Key Enhancements in SpyGlass P-2019.06-SP1-1

SpyGlass Core

The following enhancements have been made:

– Pragma Comments in .awl Files: Enhanced SpyGlass to support pragma comments in .awl files. Note that in .awl files, pragma comments can be specified with the # character only unlike in .swl files where pragma comments can be specified with both # and // characters. This support is available only for block waiver pragmas in .awl files. Inline waiver pragmas are not supported.

– moresimple report: Enhanced SpyGlass by adding two rules, named ReportObsoleteRules and ReportDeprecatedRules, to report obsolete and deprecated rules specified in a SpyGlass run in the moresimple.rptreport by default. Previously, SpyGlass generated a Warning message on the screen only if an obsolete or deprecated rule is included in a SpyGlass run.

SpyGlass CDC

The following enhancement has been made:

– Ac_coherency06a: Enhanced SpyGlass CDC by adding a rule, named Ac_coherency06a, to report signals that are synchronized multiple times in the same clock domain within same sequential depth. In addition, a parameter, named coherency_seq_depth, is introduced that controls the number of sequential elements beyond which the common source is detected by the Ac_coherency06a rule.

Synopsys’ SpyGlass RTL signoff solution is a design and coding guideline checker that delivers full chip mixed-language (Verilog, VHDL and SystemVerilog) and mixed representation (RTL & gate) capabilities to speed development of complex system-on-chip (SoC) designs. SpyGlass’ GuideWare methodology, greatly enhances the designer’s ability to check HDL code for synthesizability, simulatability, reusability, clock domain crossings, low power, timing constraints, testability and RTL/gate signoff. SpyGlass also integrates industry-standard best practices, as well as Synopsys’ own extensive experience working with industry-leading customers.

Here’s how you can quickly run SpyGlass Lint checks on your design.

Synopsys, Inc. is the world leader in electronic design automation (EDA) software for semiconductor design. The company delivers technology-leading semiconductor design and verification platforms and IC manufacturing software products to the global electronics market, enabling the development and production of complex systems-on-chips (SoCs). Synopsys also provides intellectual property and design services to simplify the design process and accelerate time-to-market for its customers. Synopsys is headquartered in Mountain View, California and has offices in more than 60 locations throughout North America, Europe, Japan and Asia.

Product: Synopsys SpyGlass

Version: vP-2019.06 SP1.1 with Documentation

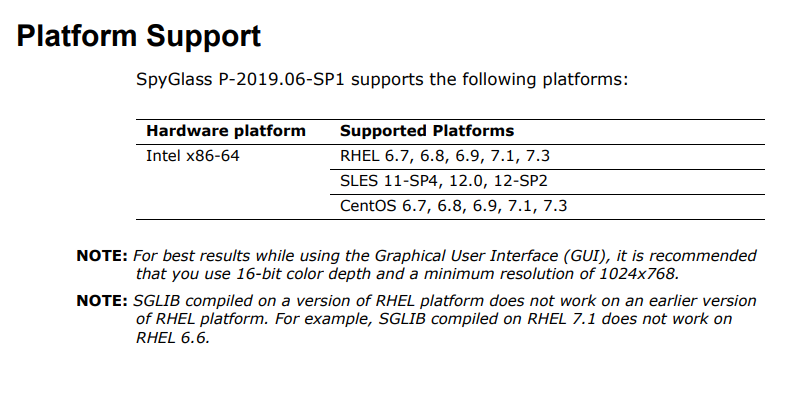

Supported Architectures: x86_x64

Website Home Page : http://www.synopsys.com

Languages Supported: english

System Requirements: Linux *

Size: 8.2 Gb

* System Requirements:

Password/解压密码www.tbtos.com