Published 7/2025

MP4 | Video: h264, 1280×720 | Audio: AAC, 44.1 KHz, 2 Ch

Language: English | Duration: 3h 31m | Size: 1.56 GB

Understand LCD display and build a VHDL controller from scratch with multiple Labs for practice

What you’ll learn

Acquire skills to read and interpret a technical datasheet

Understand the internal structure of HD44780-compatible LCDs

Design a synthesizable LCD controller in VHDL

Structure your design using finite state machines (FSMs)

Manage multiple interacting FSMs

Best practices for modular, reusable, VHDL design

Hands-on practical labs (display text, display custom character, user-configurable countdown timer)

Requirements

Basic notions on digital electronics and VHDL are needed to get the most from this course

Description

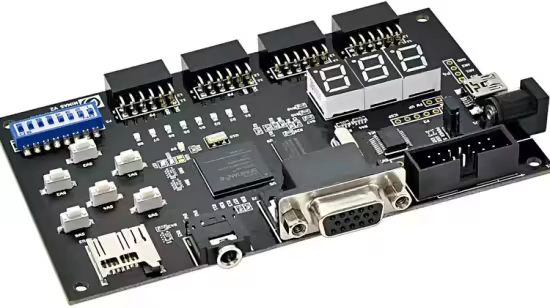

As part of the “FPGA Design Using VHDL” hands-on series, this module focuses on driving character LCD displays — a fundamental interface for embedded systems and user interaction.In this course, you will:Learn how to read and interpret an LCD datasheetUnderstand the internal architecture of an LCD (DDRAM, CGRAM, CGROM, and instruction set)Design and implement a fully functional LCD controller in VHDLLearn how to connect and map LCD pins to your FPGA using proper I/O constraintsApply theoretical knowledge through practical design labsPractice LabsLab 1: Create a simple demo that displays “HELLO WORLD” using your VHDL LCD controllerLab 2: Generate and display a custom character (like a smiley face) on the LCDLab 3: Design a configurable countdown timer displayed in real-time on the LCD, with user input through buttons and switchesBy the end, you’ll have the skills to read and understand a technical datasheet and integrate LCD displays into real-world VHDL projects with structured, reusable, and synthesizable code.Throughout the course, you’ll also strengthen your understanding of Finite State Machines (FSMs) and learn to design multiple cooperating FSMs in a single FPGA system. You will practice interfacing, timing, and structuring logic for clarity and reliability — skills essential for professional digital design.

Password/解压密码www.tbtos.com

转载请注明:0daytown » Learn FPGA design with VHDL : Driving an LCD Display