MP4 | Video: h264, 1280×720 | Audio: AAC, 44.1 KHz

Language: English | Size: 2.82 GB | Duration: 6h 47m

Fundamentals, levels of design description, Datatypes, test benchs, Tasks & system tasks, FSM with examples & Projects

What you’ll learn

Learning Verilog HDL Programming fundamental concepts and properties compare to C Language, feature & advantages of Verilog HDL over VHDL

VLSI Design flow ( FPGA & ASIC) and Difference between FPGA vs ASIC

Different design methodologies in Verilog HDL programming with examples

Behavioral modeling with blocking & Non-Blocking concepts and real time examples

Test bench Verilog program with examples

Task & system tasks with examples for random data generator, file based operations and memory load operations, and file representation input & output etc.

Finite state machine (FSM) with example for both Mealy & Moore and Sequence detector FSM

Complete design & test bench programming for Memory controllers

Complete design & test bench programming for FIFO controller

Complete design & test bench programming for Encoder & decoder for Hamming code Error detection correction

Basics of FPGA

Requirements

Intension to learn

basic in C Language

basics in Digital design ( not compulsory)

Description

Complete Verilog HDL programming course with a perfect, well structured and concise course for freshers and experienced, as it is from fundamental level to the application level. This course discuss the concepts in Verilog HDL programming and properties compared with C-Language and discussing the features and advantages.

In this course we give information related to VLSI design flow for FPGA & ASIC and gives overview about both.

This course gives information on different styles of programming like Gate level, Data flow, Behavioral and switch level with examples.

This course gives clear picture on verification, i.e. simulation and writing a test bench and some general examples like counter, clock diver using counter, pulse generator.

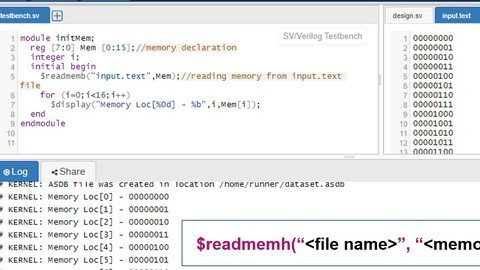

This courses explains how to write verification models using test benches with task and system tasks with Examples. These examples includes, file based system tasks such as writing data in to file, reading data from file and loading data in to memory and random data generator.

This courses shows clear picture on Finite State Machines (FSM)

how to draw,

how to realize it in to hardware model

how ro translate in to verilog code for both Mealy & Moore FSM with examples.

This course also shows some projects like Memory controller, FIFO controller and Error detection & correction using Hamming code, this improves ability to analyse and approach to Projects.

Finally it gives basic knowledge on FPGA’s like core concept how bit file is loaded in to FPGA.

Who this course is for

Undergraduate Electronics and computer science engineering students

Graduate students who planning their career in VLSI domain front end (Design & verification)

Advanced under graduate students, who willing to do project in front end VLSI design

Password/解压密码www.tbtos.com

转载请注明:0daytown » Verilog HDL programming with practical approach